- 传感器有望挑战更小尺寸,3DIC成为缩小传感器IC新解方

- 来源:赛斯维传感器网 发表于 2017/2/14

系统工程师在开发复杂的电子产品,例如传感器和传感器接口应用时,他们所面临的重大挑战为更小的外形尺寸、杰出的功能、更佳的效能及更低的物料列表成本(BoM)。 设计者可以采用具有较高整合密度的较小制程节点来缩减晶方尺寸,同时也能使用先进的封装技术来实现系统小型化。

3DIC成为缩小传感器IC新解方

对于更高系统整合度的需求持续增加,这不只促使传统的组装服务供货商,也推动半导体公司开发更创新和更先进的封装技术。 最具前景且最具挑战性的技术之一就是采用硅通孔(TSV)的三维积体(3DIC)。 3DIC技术现在已被广泛用于数字IC(例如,内存IC、影像传感器和其他组件的堆栈)中,其设计和制造方法已经在数字世界中获得成功证明。 接下来,设计者要如何将3DIC技术成功导入以模拟和混合讯号为主的的传感器IC中?

在今日,走在前面的模拟和混合讯号IC开发商已开始意识到采用模拟3DIC设计的确能带来实质好处。 智能传感器和传感器接口产品锁定工业4.0、智能城市或物联网(IoT)中的各种应用。 在各种芯片堆栈技术中,TSV和背面重新布局层(BRDL)可用来替代传统金线接合,此技术的用处极大。

3D积体技术,特别是来自领导晶圆代工业者的特殊模拟TSV技术,在结合正面或背面重新布局层(RDL)后,由于互连更短且能实现更高的整合度,因此能以更小的占板面积提供更多功能。 特别是小尺寸的TSV封装技术(总高度在0.32mm范围内)能解决智能手表或智能眼镜等穿戴式装置的的小尺寸需求。

在不同的芯片或技术组合中,TSV技术还能提供更高水平的灵活度,例如采用45奈米制程的数字芯片中的芯片至芯片堆栈,以及在模拟晶圆(例如180nm)中,微机电(MEMS)组件或光传感器和光电二极管数组的堆栈,这只是其中的几个例子。

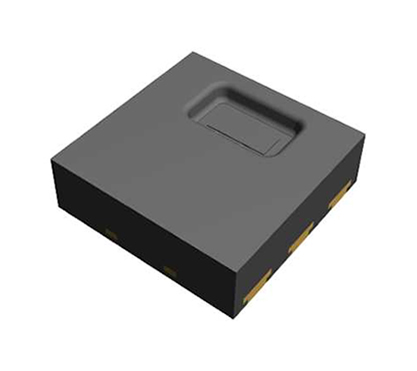

图1 采用标准打线接合的传感器芯片

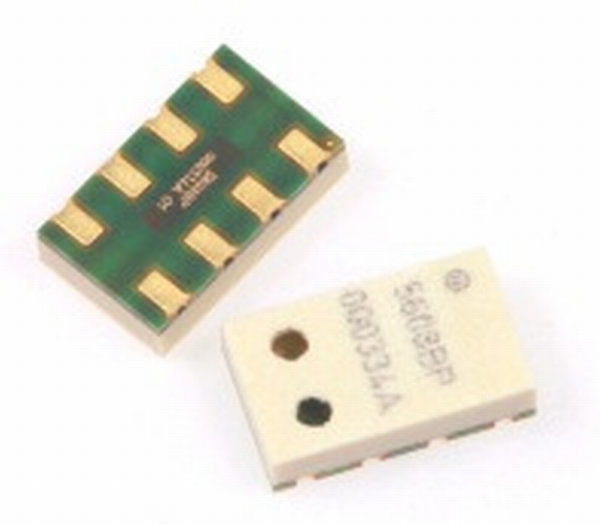

图2 采用TSV背面连接的传感器芯片

模拟3DIC技术通常是透过建造芯片正面到IC背面的电气连接来实现传感器应用。 在许多传感器应用,例如光学、化学、气体或压力传感器中,感测区域是位在CMOS侧(晶圆的顶端)。 芯片和导线架之间最常用的连接是打线接合(Wire bonding)(图1)。 无论是使用塑料封装,或是将裸片直接接合在印刷电路(PCB)或软性电路板上,对于某些会将感测区域暴露出来的应用而言,打线接合并非理想的解决方案。 采用专业晶圆代工业者的专有TSV技术,可以利用TSV、背面RDL和芯片级封装(WLCSP)(图2)来替代打线。

转载请注明来源:赛斯维传感器网(www.sensorway.cn)

- 如果本文收录的图片文字侵犯了您的权益,请及时与我们联系,我们将在24内核实删除,谢谢!