- 基于CMOS图像传感器的视频采集系统设计

- 来源:赛斯维传感器网 发表于 2011/9/26

引 言

CCD和CMOS图像传感器作为固体图像传感器领域的竞争对手,两者在性能表现上各有优劣。

相较于CCD图像传感器, CMOS图像传感器功耗低,结构简单,集成度高,体积小,成本低,这就使产品的便携性和可靠性得以极大的提高。由于CMOS图像传感器的内部结构,使其具有高抗辐照,抗干扰能力强,因此在图像传感,天文观测、小卫星、星敏感器等应用领域表现出极大的应用潜力[1]。另外基于CMOS图像传感器的加工工艺,可以较容易的制造出大面阵的CMOS体传感器器件,更加扩展了CMOS图像传感器的应用范围。

基于CMOS图像传感器的视频采集系统充分的利用了CMOS图像传感器的优点,采用USB总线供电,即插即用,电路简单,功耗低,成品体积小,成像清晰,稳定,很好的满足了CMOS图像采集系统的图像采集要求。

一.CMOS图像传感器的内部结构

目前CMOS图像传感器主要分为无源象素传感器(PPS)和有源象素传感器(APS)[2]。PPS结构简单,量子效率高,但是缺点是噪声大,并且不利于向大型阵列发展;APS在象素中加入了至少一个晶体管来实现对信号的放大和缓冲,改善了PPS的噪声问题,但恶化了阈值和增益的一致性,也减小了填充系数。

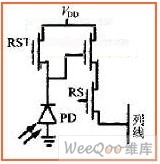

CMOS图像传感器像元结构主要有光敏二极管型无源像素结构、光敏二极管型有源像素结构(见图1)和光栅型有源像素结构,其它特殊结构还有对数传输型、钉扎光敏二极管型、浮栅放大器型等。

图1 光敏二极管型有源像素结构图

一个典型的CMOS图像传感器通常包含:一个图像传感器核心,相应的时序逻辑和控制电路、AD转换器、存储器、定时脉冲发生器和译码器等 [3] 。

定时控制电路用来设置传感器的工作模式,产生工作时序,控制数据的输出等。像素采集到的信号在芯片内部就经过了放大、AD转换、存储等处理,最后可输出需要的数字信号,也可以输出模拟信号,这给用户在设计时提供了较大的灵活性[4]。

二.CMOS图象视频采集系统工作原理

本视频采集系统整体上按照功能可以分为三个部分:CMOS成像部分、CPLD时序控制部分、USB传输部分。

整个图像采集系统的工作原理如下:通过CPLD发送正确时序信号给CMOS图像传感器,驱动其正常工作,采取合适的快门方式,并将采集到的图像数据进行打包处理,输出给USB传输芯片, USB传输芯片再将图像数据传入主机,并通过上层应用程序得到采集到的图像。

三.系统采用的主要芯片

3.1 CMOS图像传感器芯片IBIS5-A-1300。

本系统CMOS图像采集芯片选用了Fillfactory公司的IBIS5-A-1300 COMS图像传感器芯片,分辨率为1280×1024,全帧采集速率最高可达27fps,动态范围最大达到100db,6.7 m×6.7 m高填充系数像元,填充系数可达66%,支持卷帘快门和同步快门两种快门方式。内部集成可调整增益和偏置的输出放大器,以及40Msamples/s高速A/D转换模块,A/D量化等级为10bit,可直接输出模拟信号或数字信号,内部有大量的寄存器和控制器,可以对传感器的工作状态进行实时调整。芯片支持开窗技术亚采样技术,根据实际需要实时提高帧速率[5]。

3.2 数据采集芯片 EZ-USB FX2

USB传输部分选用了CYPRESS公司的EZ-USB FX2芯片,它是一个USB2.0集成外围控制器,该芯片支持12M/S的全速传输和480M/S的高速传输,可以使用(具有)4种USB传输方式:控制传输、中断传输、块传输和同步传输;该器件集成有一个增强型的8051、8.5kB的RAM、4kB的FIFO存储器、串行接口引擎(SIE)、通用可编程接口(GPIF)、I/O口、数据总线、地址总线[6]。

3.3 Altra公司的CPLD控制芯片EPM570。

系统的时序控制芯片采用Atral公司的CPLD控制芯片EPM570。该芯片可以很好的完成系统的时序控制要求。

四.CMOS视频成像系统设计

4.1系统的硬件实现。

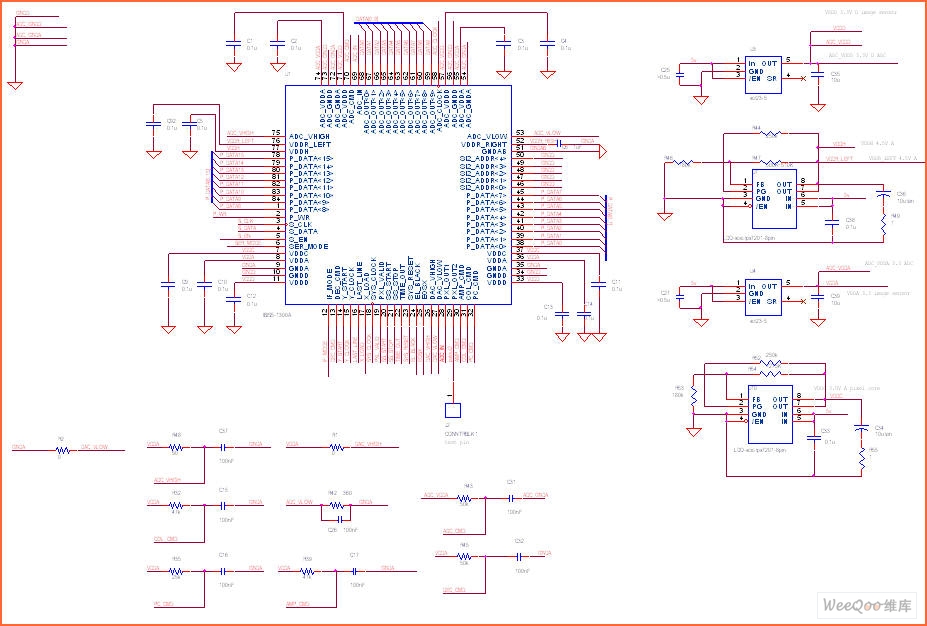

本采集系统为两块四层PCB板组合而成,其中一块为视频采集板,一块为USB数据传输板。其核心CMOS视频图像采集板如图3所示。

图3:CMOS视频图像采集板原理图

从硬件设计的原理图可以看出,CMOS图像传感器只需提供少量的电源转换器件即可正常工作,这是因为CMOS图像传感器功耗很小,只需采用USB总线提供的5v电压就可以驱动其正常工作。另外CMOS图像传感器芯片仅需要少数的几个外部控制信号即可完成图像的采集(本系统的控制信号由USB数据传输板上的CPLD芯片提供),且芯片内部集成了输出放大器,数模转换模块,只需修改芯片中的特殊寄存器值即可改变输出放大器的偏置电压,增益等参数,这样就大大降低了硬件设计的复杂度和成品的体积,具有很高的应用价值。

4.2.系统的时序设计。

CMOS图像传感器结构简单,内部集成度高,因此仅需很少的外部控制信号即可完成视频图像的采集输出

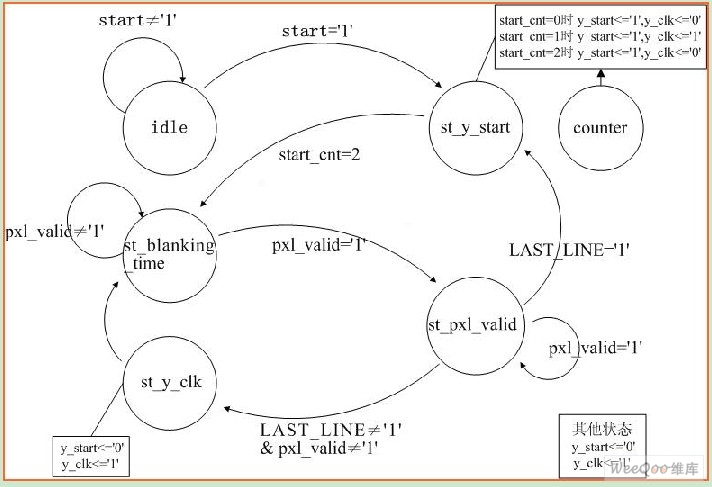

本系统时序采用VHDL硬件描述语言设计,其核心部分为一个有限状态机,具体状态关系如下

系统工作过程如下:当系统上电后,CPLD产生复位信号复位整个芯片到初始状态,然后对芯片进行并行数据注入,向CMOS图像传感器的特殊寄存器写入预定值,设置诸如像元积分时间,像素读出行数,输出放大器增益等参数。随后CPLD给CMOS芯片提供 ss_start信号,标志开始像素积分,ss_stop信号结束像素积分,随后图像传感器即处于可读出状态。向CMOS发出y_start信号开始一帧图像的读出,发出y_clock信号,开始一行图像的读出,当CMOS图像传感器有像素信号输出时, pxl_valid引脚信号为高,此时CMOS图像传感器正在进行一行图像的输出,当pxl_valid变低时,一行图像输出结束,CPLD再提供下一个y_clock信号,启动CMOS进行下一行图像的读出。当一帧图像的最后一行开始读出时,CMOS芯片的LAST_LINE引脚变高,标志一帧图像读出的结束,CPLD再产生下一个ss_start信号,开始下一帧图像的读出。这样,CMOS就在CPLD的时序控制下,正常工作,循环读出图像。

4.3.USB图像采集模块设计。

本系统的数据采集模块采用cypress公司的EZ?_USB FX2 ,USB传输芯片,通过编写固件程序,使该芯片工作在高速批量传输方式。本系统采用芯片中的SLAVE FIFO传输模式[7],即不通过USB芯片中增强型8051核控制和干预,将数据直接通过USB总线,高速的传输到pc机中。最后利用visual c++6.0编写上层用户端程序,采用多线程技术,创建两个线程:USB传输线程和图像实时显示线程,实现了在pc机中的实时图像显示。

五.试验结果

从试验拍摄的鉴别率靶图像可以看到,CMOS图像传感器成像清晰,稳定,分辨率高。整个CMOS视频采集系统结构简单,时序设计容易,开发周期短,其成品体积小,外围器件少,成本低,采用USB总线供电,即插即用,具有很高的实用价值。

转载请注明来源:赛斯维传感器网(www.sensorway.cn)

- 如果本文收录的图片文字侵犯了您的权益,请及时与我们联系,我们将在24内核实删除,谢谢!